1,这些呢在线路设计中叫零件封装和尺寸

2,在线路设计的时候首先要对零件选型,然後可以查看规格书,规格书里面就有封装了

3,例如一般电晶体,有TO-92,SOT-23,SOP-8等等

FPGA设计中的仿真有哪三种

本发明涉及芯片测试技术领域,尤其涉及一种基于fpga芯片实现的scan chain电路的测试系统及方法。

背景技术:

2.scan chain(扫描链测试)作为数字集成电路测试的重要方法之一,可以有效的筛选出坏片,提高产品质量。芯片插入scan chain进行测试的基本原理是从芯片外部设定电路中各个触发器的状态,并通过简单的扫描链的设计,扫描观测触发器是否工作在正常状态,以此来检测电路的正确性。

3.在芯片tape out前会使用dft工具在芯片内部插入scan chain,scan chain电路作为设计出来的电路,同样也需要进行仿真。在ic t/o回来后,scan chain作为测试电路,其本身电路设计的功能性及可靠性也需要做验证。在业界,通常是使用ate设备(aotuomatic test equipment)对其做测试和验证,但ate作为ic测试环节的专用设备,价格昂贵,通常ic design house不会单独购买,一般都是在ic验证后期开发cp/ft程序时,才会使用ic测试厂的ate设备去做scan chain测试方案的开发。

4.从以上的描述可以看出,scan chain电路的测试存在测试设备专业化、单一化的问题,对于小型的design house来说,to前期使用ate设备做fpga验证不方便,要么买,要么租ate设备,或者去测试厂做验证,如果只做仿真的话,又存在后仿速度非常慢的问题。

技术实现要素:

5.本发明的主要目的在于解决目前scan chain电路的测试存在测试设备专业化、单一化的问题,在提出了一种基于fpga实现的芯片scan chain电路的测试系统的同时,还提供了该测试系统的测试方法。

6.其中,一种基于fpga芯片实现的scan chain电路的测试系统,其特征在于,所述测试系统集成于fpga芯片上,包括:数据解析单元、存储单元、时序发生单元、控制单元和结果输出单元;

7.所述数据解析单元,用于将仿真生成原始scan chain电路的激励信号和原始scan chain电路的预期输出信号进行数据解析;

8.所述存储单元,对数据解析单元解析的用于scan chain电路的激励信号进行编码,确定待检测点后经过scan chain电路进行激励,并存储激励后的输出信号,还用于对数据解析单元解析后scan chain电路的预期输出信号进行编码并存储;

9.所述时序发生单元,用于发出测试scan chain电路的时序波形;

10.所述控制单元,用于按照scan chain电路的检测要求,针对激励的输出信号在时序发生单元提供的采样时序下采样,并将采样数据和存储的预期输出信号进行数据比对;

11.所述结果输出单元,用于输出控制单元比较的结果,当比对结果不一致时,则上报错误,当比对结果正确,则继续下一个周期的检测,直到经过scan chain电路后的激励信号

完全检测完毕,输出比对结果。

12.进一步地,所述结果输出单元包括对比正确结果输出单元和对比错误结果输出单元。

13.进一步地,所述系统还包括测试结果显示单元,用于根据预先定义好的输出显示时序显示比对结果。

14.本发明还提供一种基于fpga芯片实现的scan chain电路的测试方法,其特征在于,所述方法包括:

15.s1,将仿真生成原始scan chain电路的激励信号和原始scan chain电路的预期输出信号进行数据解析,并对数据解析单元解析的用于scan chain电路的激励信号进行编码,编码后经过scan chain电路进行激励,并存储激励后的输出信号,并对数据解析单元解析后scan chain电路的预期输出信号进行编码并存储;

16.s2,按照scan chain电路的检测要求,并根据测试scan chain电路的时序波形对经过编码后的scan chain电路的激励信号进行采样,并将采样数据和存储的预期输出信号进行数据比对;

17.s3,输出结果,当比对结果不一致时,则上报错误,当比对结果正确,则继续下一个周期的检测,直到激励信号完全检测完毕。

18.进一步地,s1中,对scan chain电路的激励信号进行编码和对scan chain电路的预期输出信号进行编码时是针对需要检测点的进行编码,并使两者在时间点及检测点相匹配。

19.进一步地,所述方法还包括对输出结果进行显示,在收到比较结果后,如果比较出错,则锁存该时刻点的出错信息,记录现场数据,根据预先定义好的输出显示时序,显示出错信息;若比较结果正确,则不发送出错信息,按照预先定义好的表示比对正确显示时序进行显示。

20.本发明的有益效果:

21.实现了在小型fpga平台上对scan chain电路的测试,实现方案价格便宜,测试速度快。

附图说明

22.图1为本发明实施例中的方法流程图。

具体实施方式

23.本发明实施例提供了一种快充协议测试板及其测试方法。

24.本发明的说明书和权利要求书及上述附图中的术语“第一”、“第二”、“第三”、“第四”等(如果存在)是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的实施例能够以除了在这里图示或描述的内容以外的顺序实施。此外,术语“包括”或“具有”及其任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

25.为便于理解,下面对本发明实施例的系统及方法的具体流程进行描述。一种基于fpga芯片实现的scan chain电路测试的系统,所述测试系统集成于fpga芯片上,包括:数据解析单元、存储单元、时序发生单元、控制单元和结果输出单元;

26.所述数据解析单元,用于将仿真生成原始scan chain电路的激励信号和原始scan chain电路的预期输出信号进行数据解析;

27.所述存储单元,对数据解析单元解析的用于scan chain电路的激励信号进行编码,确定待检测点后经过scan chain电路进行激励,并存储激励后的输出信号,还用于对数据解析单元解析后scan chain电路的预期输出信号进行编码并存储;需要说明的是,对scan chain电路的激励信号进行编码和对scan chain电路的预期输出信号进行编码时是针对需要检测点的进行编码,并使两者在时间点及检测点相匹配,这是由于,并不是scan chain电路中所有部分都要检测,而是特点的点需要检测,针对这些特定的点,需要做标记,所以才需要编码。

28.所述时序发生单元,用于发出测试scan chain电路的时序波形,使用状态机实现,根据存储单元存储的波形文件,发出测试scan chain的时序波形;

29.所述控制单元,用于按照scan chain电路的检测要求,针对激励的输出信号在时序发生单元提供的采样时序下采样,并将采样数据和存储的预期输出信号进行数据比对;

30.所述结果输出单元,用于输出控制单元比较的结果,当比对结果不一致时,则上报错误,当比对结果正确,则继续下一个周期的检测,直到仿真的经过ate设备后的激励信号完全检测完毕,输出比对结果。

31.需要说明的是,所述结果输出单元包括对比正确结果输出单元和对比错误结果输出单元,通过两个输出通道输出不同的检测结果,所述系统还包括测试结果显示单元,用于根据预先定义好的输出显示时序显示比对结果,用于分别显示对比正确结果输出单元和对比错误结果输出单元。

32.请参阅图1,本发明实施例中基于fpga芯片实现的scan chain电路测试方法的实施例,包括:

33.s1,将仿真生成原始scan chain电路的激励信号和原始scan chain电路的预期输出信号进行数据解析,并对数据解析单元解析的用于scan chain电路的激励信号进行编码,编码后经过scan chain电路进行激励,并存储激励后的输出信号,并对数据解析单元解析后scan chain电路的预期输出信号进行编码并存储;

34.s2,按照scan chain电路的检测要求,并根据测试scan chain电路的时序波形对经过编码后的scan chain电路的激励信号进行采样,并将采样数据和存储的预期输出信号进行数据比对,比对时使两者在时间点及检测点相匹配;

35.s3,输出结果,本实施例中是按照scan chain的check要求,在测试scan chain电路的时序波形scan clk的上升沿来时,采样scan data,并和存储的数据比对,如果比对结果不一致则上报错误,如果比对正确,则继续下一个cycle的check,直到scan data check完毕,输出比对结果;

36.所述方法还包括对输出结果进行显示,在收到比较结果后,如果比较出错,则锁存该时刻点的出错信息,记录现场数据,根据预先定义好的输出显示时序,显示出错信息;若比较结果正确,则不发送出错信息,按照预先定义好的表示比对正确显示时序进行显示。

37.以上所述,以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

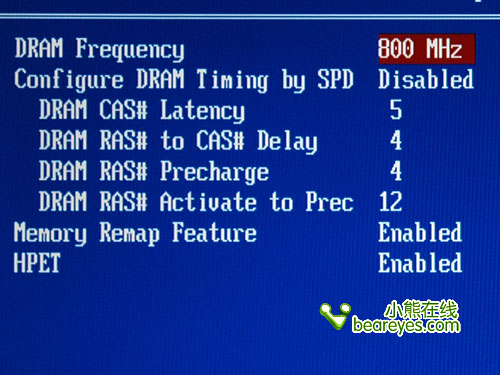

FPGA设计中的仿真有:

1、RTL级行为仿真(又称作为功能仿真、前仿真);

2、综合后门级仿真;

3、时序仿真(又称为后仿真)。

第一个仿真可以用来检查代码中的错误以及代码行为的正确性,其中不包括信息。如果没有实例化一些与器件相关的特殊底层元件的话,这个阶段的仿真也可以做到与器件无关。

第二个仿真绝大多数的综合工具除了可以输出一个标准网表文件以外,还可以输出Verilog或者VHDL网表,其中标准网表文件是用来在各个工具之间传递设计数据的,并不能用来做仿真使用。

输出的Verilog或者VHDL网表可以用来仿真,综合工具给出的仿真网表已经是与生产厂家的器件的底层元件模型对应起来了,为了进行综合后仿真必须在仿真过程中加入厂家的器件库,对仿真器进行一些必要的配置,不然仿真器并不认识其中的底层元件,无法进行仿真。

第三个仿真在设计布局布线完成以后可以提供一个时序仿真模型,这种模型中也包括了器件的一些信息,同时还会提供一个SDF时序标注文件。

扩展资料

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

现场可编程门阵列是可编程器件,与传统逻辑电路和门阵列相比,FPGA具有不同的结构。FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O。

由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

参考资料:

百度百科-FPGA

百度百科-若贝FPGA仿真

百度百科-FPGA设计