Jk触发器JK (Jump-Key)flip-flop RS触发器RS (Reset-Set) flip-flopT触发器T (Toggle) flip-flop

JK触发器是数字电路触发器中的一种电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。

D触发器的状态方程是:Q*=D,JK触发器的状态方程是:Q*=JQ'+K'Q。

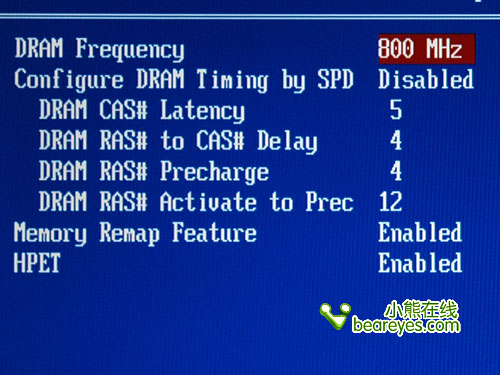

D触发器有两种触发方式:电平触发和边缘触发。前者可以在CP(时钟脉冲)等于1时触发,后者主要在CP的前面触发(正跳0→1)。

D触发器的二次状态取决于D端触发前的状态,即二次状态=D,因此具有设置0和1的两个功能。对于边缘D触发器,电路在CP=1时具有保持阻塞的功能,因此在CP=1时,D端数据状态的变化不会影响触发器的输出状态。

工作过程如下:

1、CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5非=D非。

2、当CP由0变1时触发器翻转。这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。Q3=Q5非=D非,Q4=Q6非=D。由基本RS触发器的逻辑功能可知,Q=Q3非=D。

总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。与主从触发器相比,同工艺的边沿触发器有更强的抗干扰能力和更高的工作速度。 /span>。由基本RS触发器的逻辑功能可知,Q=Q3非=D。