74LS139片内就是双2线-线译码器,正好组成三输入两输出的奇偶校验电路。

在数据选择器中,通常用地址输入信号完成挑选数据的任务。如一个4选1的数据选择器,应有2个地址输入端。共有2z=4种不同的组合,每一种组合可选择对应的一路输入数据输出。同理对一个8选1的数据选择器,应有3个地址输入端。

扩展资料:

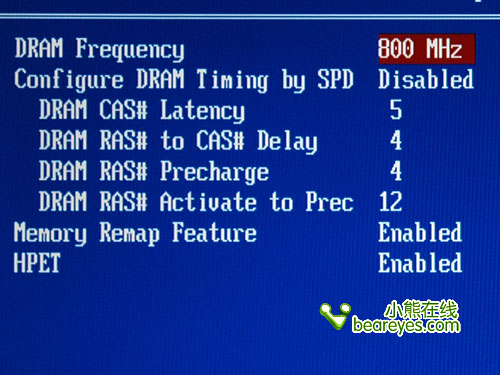

为了能检测和纠正内存软错误,首先出现的是内存“奇偶校验”。内存中最小的单位是比特,也称为“位”,位只有两种状态分别以1和0来标示,每8个连续的比特叫做一个字节(byte)。不带奇偶校验的内存每个字节只有8位,如果其某一位存储了错误的值,就会导致其存储的相应数据发生变化,进而导致应用程序发生错误。而奇偶校验就是在每一字节(8位)之外又增加了一位作为错误检测位。

百度百科-奇偶校验

什么是奇偶校验电路

设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要3个异或门。

奇偶校验(Parity Check)是一种校验代码传输正确性的方法。根据被传输的一组二进制代码的数位中“1”的个数是奇数或偶数来进行校验。采用奇数的称为奇校验,反之,称为偶校验。采用何种校验是事先规定好的。通常专门设置一个奇偶校验位,用它使这组代码中“1”的个数为奇数或偶数。若用奇校验,则当接收端收到这组代码时,校验“1”的个数是否为奇数,从而确定传输代码的正确性。

奇偶校验电路是一种校验代码传输正确性的电路。 奇校验电路,当输入有奇数个1时,输出为1;偶校验电路当输入有偶数个1时,输出为0。奇偶校验只能检查一位错误,且没有纠错的能力。 奇校验是通过增加一位校验位的逻辑取值,在源端将原数据代码中为1的位数形成奇数,然后在宿端使用该代码时,连同校验位一起检查为1的位数是否是奇数,做出进一步操作的决定。 奇偶校验器多设计成九位二进制数,以适应一个字节,一个ASCII代码的应用要求。

奇偶校验是一种冗余编码校验,在存储器中是按存储单元为单位进行的,是依靠硬