4-16位的译码器编写方法是:对0000—0111的输入信号进行译码输出,将两片3线—8线译码器连接成4线—16线译码器,其中第二片74138的使能端G1和第一片的使能端G2A接成D输入端。

当D=0时,第一片74138工作,对0000—0111的输入信号进行译码输出。当D=1时,第二片74138工作,对1000—1111的输入信号进行译码输出。其输出为低电平有效,使能端G1为高电平有效,/G2/G3为低电平有效,当其中一个为低电平,输出端全部为1。

4-16位译码器的使用要求:

1、输出为低电平有效,故实现逻辑功能时,输出端不可接或门及或非门(因为每次仅一个为低电平,其余皆为高电平)。

2、用4个输入线写出输出线的地址,使得在一个选通输入为低时数据通过另一个选通输入。当任何一个选通输入是高时,所有输出都为高。

用两片74ls138也可以组成4/16译码器-20151030方法是:

通过真值表,我们可以发现,用两片74LS138组合成4/16译码器原理关键在于D4。

D4为0:打开1号,关闭2号。1号是16位数据的低字节,2号是16位数据的高字节。高字节默认为0XFF,低字节由1号控制,显示Y0-Y7。

D4为1:打开2号,关闭1号。1号是16位数据的低字节,2号是16位数据的高字节。低字节默认为0XFF,高字节由2号控制,显示Y8-Y15。

两片74LS138组成的4-16线译码器工作原理求解

将双3-8译码器级联为4-16译码器。

设计思路

由于译码器译码输入与输出对应,输入端位0000~1111对应选择输出端的Q0~Q15,且0000~0111恰好对应Q0~Q7,故可以根据输入端最高位将4-16线译码器分割为低8位和高8位,

结合逻辑地址分段的思路使用两个3-8线译码器的表示对应的Q0~Q7和Q8~Q15。

由于Q0~Q7和Q8~Q15除了输入端的最高位不同其余位数对应相等,因此可以通过使用输入端最高位控制3-8译码器的使能端来选择输出端口的段地址,通过剩余的输入作为偏移地址控制有效译码器的输出。

设计分析

该设计通过输入端最高位作为片选信号作为分段的选择,将输入端剩余位数作为偏移量选择片内输出,实现两个3-8译码器的级联形成4-16译码器。

注意事项

译码器根据其内部结构不同输出端和使能端均有高电平有效和低电平有效两种,实际使用应根据相关技术手册调整,即调整反相器的位置和输出的默认电平,常使用上拉电阻和下拉电阻。

先取第1片74LS138的和作为它的第四个地址输入端(在同一个时间令),再取第2片74LS138的和作为它的第四个地址输入端(在同一个时间令),最后取两片的和,并将两片74LS138相接,于是得到两片74LS138的输出分别为:

上面的两式表明了第1片74LS138工作而第2片74LS138禁止时,将的0000~0111这8个代码译成8个低电平信号;第2片74LS138工作而第1片74LS138禁止时,将的1000~1111这8个代码译成8个低电平信号。

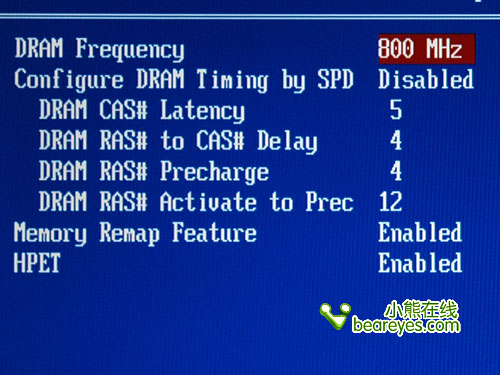

这样就用两个3线-8线译码器74LS138扩展成一个4线-16线的译码器了,电路原理图如下图所示:

扩展资料:

74LS138 为3线-8线译码器,共有 54LS138和 74LS138 两种线路结构型式。其中,54LS138为军用,74LS138为民用。其工作原理为:

1、当一个选通端(E1)为高电平,另两个选通端((/E2))和(/E3))为低电平时,可将地址端(A0、A1、A2)的二进制编码在Y0至Y7对应的输出端以低电平译出。(即输出为Y0至Y7的非)比如:A2A1A0=110时,则Y6输出端输出低电平信号。

2、利用 E1、E2和E3可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

3、若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器。

4、可用在8086的译码电路中,扩展内存。

百度百科-74LS138

两片74LS138组成的4-16线译码器工作原理是利用使能端组成的。选择端输入为D0,D1,D2,使能端变为选择端D3。74ls138的使能端芯片使能时,必须是 S1=H,S2+S3=L;也就是S1为高电平时,S2和S3同时为低电平时芯片才被使能,否则芯片输出全是H。当输入D3为L时,74ls138(1)被使能,74ls138(2)的输出全为H,74ls138(1)会根据D0,D1,D2的输入信号选择出输出L的输出端。当输入D3为H时,74ls138(2)被使能,74ls138(1)的输出全为H,74ls138(2)会根据D0,D1,D2的输入信号选择出输出L的输出端。此就为4 - 16线译码原理。