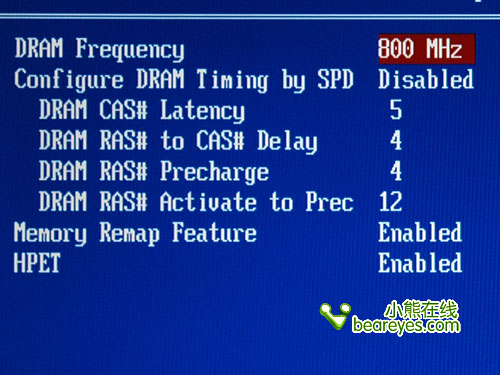

不知道是什么教育层次的作业,我就按实际电路分析吧。

D型触发器做2分频,时钟上升沿出发,输出Q波形很简单。有意思的是后面的门电路。触发器用的是CMOS器件,我只能推断门电路也是CMOS器件,那么,由于CMOS电路输入阻抗很高,RC构成的积分电路就会起一定的延时作用,而输入信号频率又很低,所以总输出VO在Q输出的上升沿会输出“0”电平的窄脉冲。如果除去RC电路,VO输出一直是高电平。?

如果题目真的是用RC电路控制输出脉冲宽度,我认为老师出这个题目不妥,太脱离实际了,RC定时是不稳定的,会误导学生的。