1、工作环境,例如温度,湿度,温差等等

2、干扰,例如通信电磁干扰,地磁干扰,太阳黑子活动干扰等

3、电路板设计合理性,包括地线处理,高频隔离保护,布线干扰等

4、元器件可靠性,元器件寿命,元器件可靠性等级,例如民用级、工业级和军用级等

5、机箱内部布局,包括背板线路合理性,电源布局合理性,散热布局合理性,信号干扰控制等。

(1)、高速电路引起的可靠性问题主要有以下 5 个方面:

信号传输延时逐步加大,造成时序失效。

信号波形失真逐步加大,造成信号读取错误。

信号之间的串扰逐步加大,产生误码或程序运行错误。

电源质量和地弹逐步变坏,影响器件的正常工作。

EMC指标逐渐超过要求。

(2)、 3 种可靠性技术来解决办法:

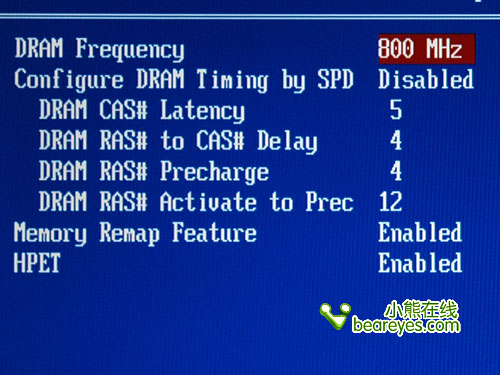

A、运用最坏情况分析(WCCA)方法,进行数字电路时序分析,使传输线延时、在整个生命周期内不超过要求,保证高速数字电路的正常逻辑连接。

数字电路时序容差分析主要是分析数字电路间的时序关系,即分析时序余量是否满足要求。为了分析该电路的时序容差情况,主要考虑三个方面的因素:器件本身的时序参数容差、 PCB布线产生的时序容差、其他干扰产生的时序容差。PCB 布线产生的时序容差分析主要是分析器件端口模型、传输线拓扑、终端匹配、负载数量等在最坏情况下,采用信号完整性(SI)仿真工具,分析传输信号延时和波形,得出对时序的影响。其他干扰产生的时序容差分析主要是分析电源输入、电源平面谐振特性、同步开关噪声、 ISSI噪声、串扰等对信号时序的影响。时序参数中最关键的是建立时间和保持时间两个参数。?

B、运用仿真和实验相结合的方法,准确分析出串扰源和耦合途径。

感性串扰和容性串扰的相同点是:串扰在远端为短脉冲,近端为长信号。不同之处是:前向感性串扰和前向容性串扰的极性相反(如下图 2),感性串扰产生的是噪声电压信号,是串接在被干扰导线上的,而容性串扰产生的是噪声电流信号,是并接在被干扰导线和地之间的,也就是说,感性串扰随负载增大而减小,容性串扰随负载增大而增大。

C、运用电源完整性(PI)方法,分析电源输出滤波电路和电源平面设计,保证整个生命周期内的电源都符合要求。

(3)、高速电路设计相关高速电路中的 EMC 问题、低噪声设计、信号完整性(SI)、RF 设计等一直是国内工程师面临的最大挑战。