前段开发还是后端的?

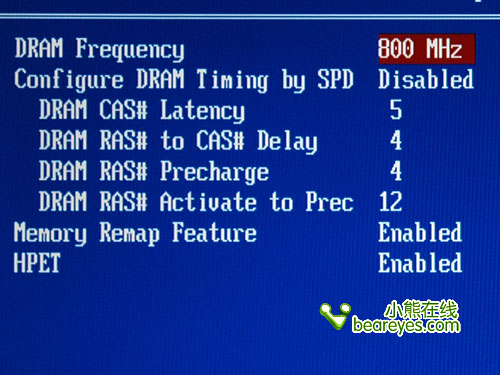

所谓的前端,主要是根据各种spec,进行RTL代码的编写,还有算法分析,power的分析等,都属于

后端主要是综合以后,layout什么的,到了版图级别了。

选器件是在项目初期,定性的时候。。。。。

2,在一般FPGA工程师平时工作中遇到的程序设计都是大型的吗?还是中小型居多。

(本人是个菜鸟选手,想了解对于一个FPGA工程师来说要具备什么条件。比如VERILOG语言能够会到什么程度)

首先,一个SOC项目肯定很大,每个人都是负责一个或者几个模块,如果初学,可能从简单的外设开始,慢慢的变的复杂,当然如果公司缺人,可能一个人从前端到后端,从模拟到数字都得整。

所以工程么,大小得看你负责的部分了。哪个公司、哪个实验室不想做大项目啊

至于verilog,你要用其来描述电路,如果一个合格的硬件设计工程师,你在写verilog的时候,脑子里必须知道你描述的电路综合出来是什么!!!!!

所以程度,还是越高越好,要不,你的电路不管是性能还是其他的都有缺陷的,仿真器的优化也是有限的。

加油~~~谢谢