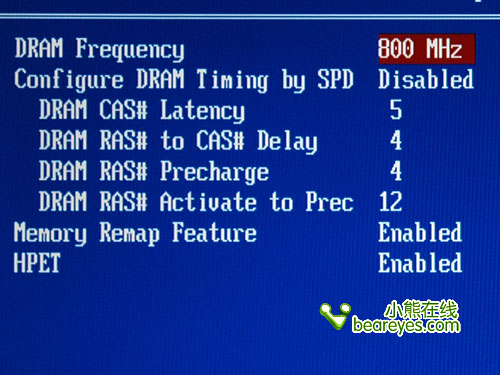

你的程序的主要的问题就是:

1.你写的是时序逻辑,里面用到的reg类型的变量在正常使用之前是要初始化的,否则用modulesim仿真时会一直为红线"X"状态的。

2.写常量数字时,一定要加上宽度,如果你只写一个“1”,那么这个1就默认为是32位的,很耗资源。

3.除非你对`timescale在仿真时的冲突决策很了解,否则建议你只在Testbench中使用这个宏。

以下是我修改过的程序,我仿真过了,没问题:

module fenpinqi(

div12,

clk,

rst

);

input clk;

input rst;

output div12;

reg div12;

reg [2:0] cnt;

always @(posedge clk)

begin

if (rst == 1'b0)

begin

div12 <=1'b0;

cnt <='b0;

end

else

begin

if(cnt==3'b101)

begin

div12 <= ~div12;

cnt <= 'b0;

end

else

begin

cnt <= cnt + 1'b1;

end

end

end

endmodule

//*******************************************************

`timescale 1ns/1ns

module

fenpinqi_tb;

reg clk;

wire div12;

reg rst;

fenpinqi u3cs(

.clk(clk),

.div12(div12),

.rst(rst));

initial

begin

clk=1'b0;

rst=1'b0;

#30 rst=1'b1; end

always

begin

#10 clk=1'b1; #10 clk=1'b0;

end

endmodule