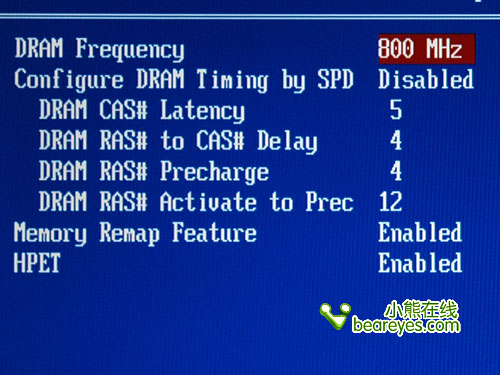

异步电路:主要是组合逻辑电路,用于产生地址译码器、FIFO或RAM的读写控制信号脉冲,但它同时也用在时序电路中,此时它没有统一的时钟,状态变化的时刻是不稳定的,通常输入信号只在电路处于稳定状态时才发生变化。也就是说一个时刻允许一个输入发生变化,以避免输入信号之间造成的竞争冒险。电路的稳定需要有可靠的建立时间和持时间,待下面介绍。同步电路:是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有操作都是在严格的时钟控制下完成的。这些时序电路共享同一个时钟CLK,而所有的状态变化都是在时钟的上升沿(或下降沿)完成的。比如D触发器,当上升延到来时,寄存器把D端的电平传到Q输出端。在同步电路设计中一般采用D触发器,异步电路设计中一般采用Latch修改

同步整流电路原理

同步整流电路是一种使用与输入电压或电流同步的方法来实现整流的电路。它通常由一个变换器和一个整流器组成。变换器可以将交流电转换成直流电,而整流器则可以将输出电压或电流中的不稳定因素去除。这种方法可以提高效率,并且可以用来控制电流或电压的幅度和相位。