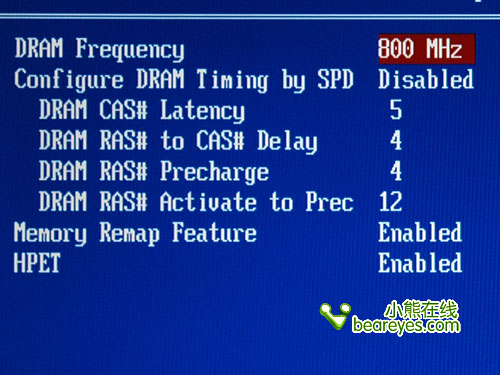

乘法器电路的关键路径是指同步逻辑电路中,组合逻辑时延最大的路径。这是一种用于两个数字相乘的电路,是需要用这样的路径进行运算的。乘法器电路中的设计性很重要,这就对是对设计性能起决定性影响的时序路径。

乘法器电路的关键路径是指

路径在图论中的定义为从一点出发,沿支路运动,到达另一点,中间所经过的节点只经过一次,称这两点间的一条路径。

你的问题不够明确。若只讨论并联电路两端的两个节点之间的路径,显然,并联的支路有多少,这两点间的路径就有多少。

整个硬件电路时序的关键路径。关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我认为还需要加上布线的延迟),也就是说关键路径是对设计性能起决定性影响的时序,通常乘法器处于关键延时路径上,因此乘法器的速度对整个系统性能有重要影响。